Berichten zufolge hat Samsung Electronics zum ersten Mal weltweit erfolgreich einen DRAM-Arbeitswafer auf Basis der 4F²-Architektur hergestellt und damit die physische Schrumpfungsgrenze durchbrochen, mit der herkömmliche planare DRAMs seit langem konfrontiert sind. Es wird berichtet, dass Samsung im Februar dieses Jahres diesen 16-Gb-DRAM-Prototyp mit integrierter 4F²-Architektur erstmals auf der ISSCC 2026-Konferenz öffentlich vorgeführt hat.

Samsung hat die Waferproduktion im 10a-Verfahren im März abgeschlossen und den normalen Betrieb des Wafers durch charakteristische Tests bestätigt. Diese Errungenschaft ist die weltweit erste Praxis der Integration der 4F²-Zellenstruktur und der Vertical-Channel-Transistor-Technologie (VCT).

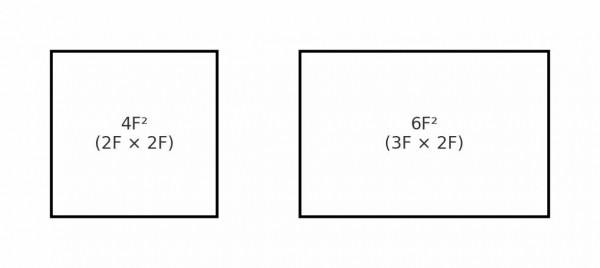

Technisch gesehen reduziert die 4F²-Architektur die Flächeneinheit eines herkömmlichen DRAM von 6F² auf eine quadratische Struktur von 2F×2F, wodurch die Kapazität pro Flächeneinheit theoretisch um 30 % bis 50 % erhöht werden kann, während die Vorteile von Geschwindigkeit und Stromverbrauch berücksichtigt werden.

Um diese Struktur zu realisieren, führte Samsung die VCT-Technologie ein, um den Transistorkanal vertikal aufzurichten und die Kanallänge innerhalb der begrenzten Chipfläche zu erhöhen, wodurch der Kurzkanaleffekt und die Leckageprobleme, die bei herkömmlichen Planartransistoren während der Skalierung auftreten, effektiv gemildert werden.

Andererseits nutzt Samsung die Inter-Wafer-Hybrid-Kupfer-Bonding-Technologie, um das Speicherzellenarray und die Peripherieschaltkreise auf verschiedenen Wafern zu trennen und sie dann vertikal zu stapeln, um eine Verbindung mit ultrahoher Dichte zu erreichen.

Das Kanalmaterial wurde ebenfalls von herkömmlichem Silizium auf Indium-Gallium-Zinkoxid (IGZO) umgestellt, um Leckströme in schrumpfenden Zellen zu unterdrücken.

Zukünftig können DRAM-Chips gleicher Größe in mehr Einheiten gepackt werden. Von Endgeräten wie dünnen und leichten Notebooks und Smartphones wird erwartet, dass sie bei geringer Größe und geringem Stromverbrauch eine größere Speicherkapazität und einen schnelleren Datendurchsatz erreichen.

Samsung hat hierfür einen klaren Fahrplan geplant: Abschluss der 10a-DRAM-Entwicklung im Jahr 2026, Durchführung von Qualitätstests im Jahr 2027 und Übergang zur Massenproduktion im Jahr 2028.

SK Hynix plant die Einführung von 4F²+VCT am 10b-Knoten, während Micron die bestehende Designroute beibehält. Chinesische Hersteller setzen aufgrund von EUV-Beschränkungen direkt 3D-DRAM ein.