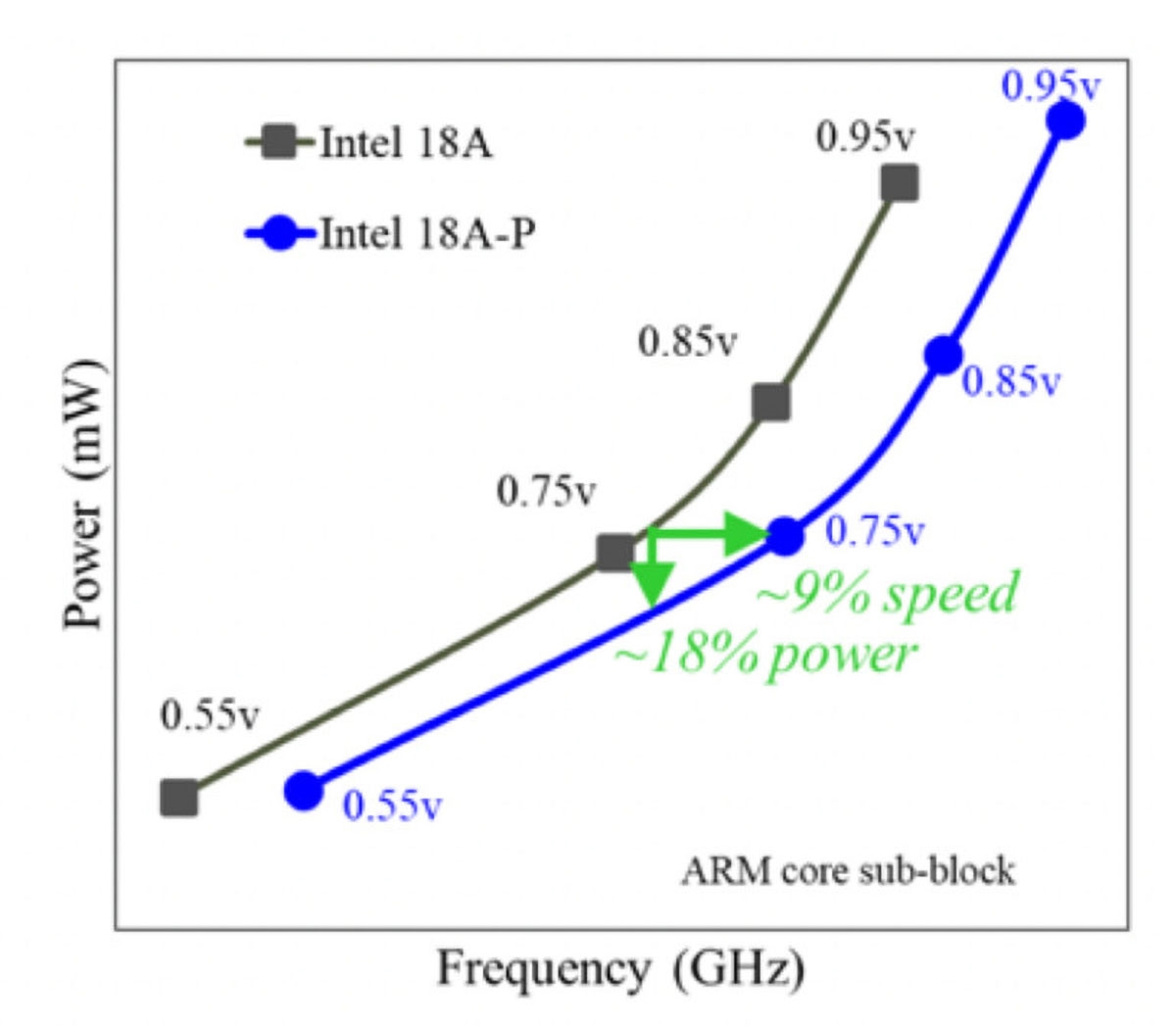

Intel hat die wichtigsten technischen Daten des Intel 18A-P-Prozessknotens offiziell im Paper T1.2 auf dem VLSI 2026-Seminar in Honolulu, Hawaii, bekannt gegeben. Im Vergleich zum standardmäßigen Intel 18A-Knoten erzielt 18A-P bei gleichem Stromverbrauch einen Leistungsgewinn von mehr als 9 % und reduziert den Stromverbrauch bei gleicher Leistung um mehr als 18 %.

Diese Arten von Leistungs- und Leistungsverbesserungen, die normalerweise nur bei generationsübergreifenden Knotenübergängen zu beobachten sind, können jetzt mit dem 18A-P bei gleicher Dichte erreicht werden.

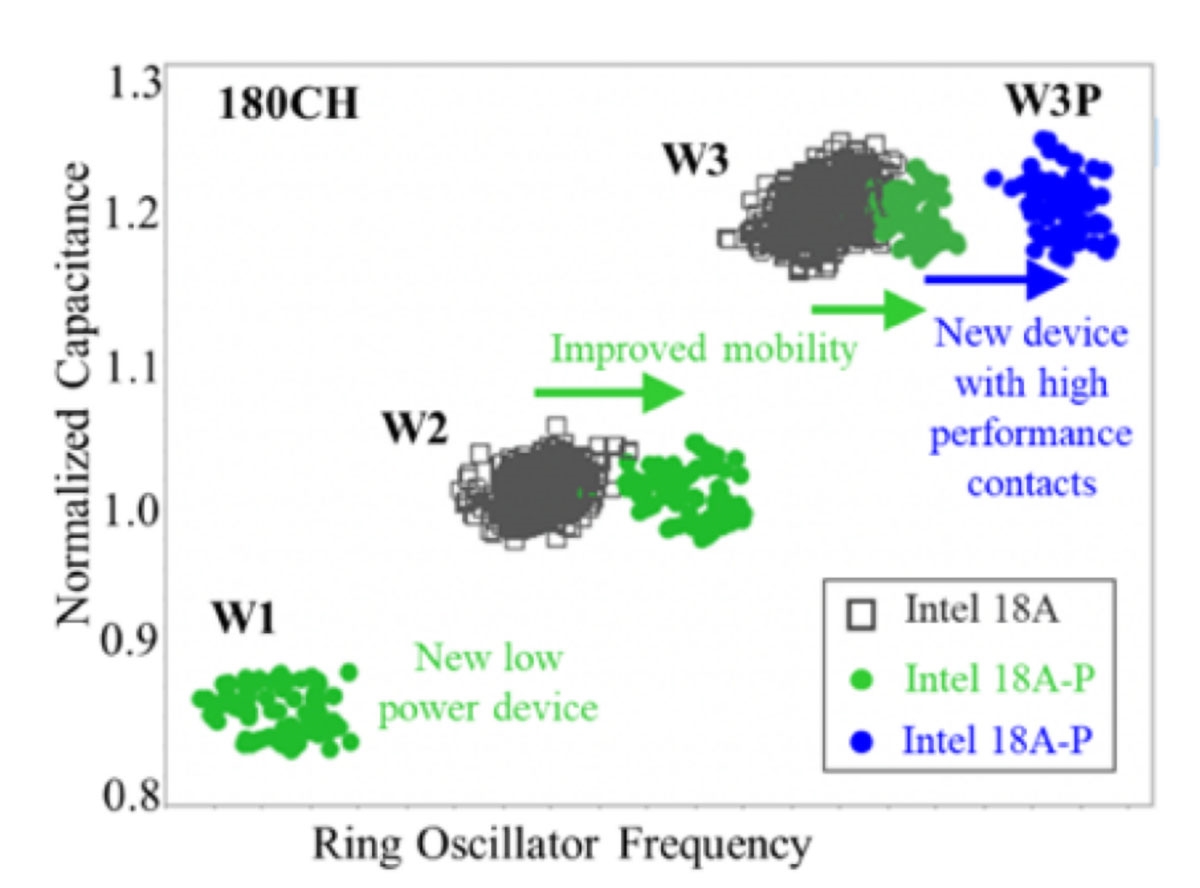

Das ursprüngliche Intel-Papier listet vier spezifische Verbesserungen auf: zusätzliche logische VT-Paare, engere Steuerung des Taktversatzwinkels, neue Geräte mit geringem Stromverbrauch in High-Density- (HD) und High-Performance-Bibliotheken (HP) sowie leistungsgesteigerte Versionen von HP-Geräten in beiden Bibliotheken.

Intel hat die Skew-Ecken von 18A-P im Vergleich zum Standard-18A um etwa 30 % verringert. Der Leistungsunterschied zwischen Transistoren auf demselben Wafer wird erheblich verringert, der Stromverbrauch und die Leistungsmerkmale sind besser vorhersehbar und gleichzeitig werden die Parameterausbeute und die Chipkonsistenz verbessert.

Im Hinblick auf die Wärmeableitung ist der Wärmewiderstand von 18A-P etwa 50 % niedriger als der von 18A, und die Wärmeleitfähigkeitseffizienz wird erheblich verbessert. Dies ist besonders wichtig für den dauerhaften Hochfrequenzbetrieb in Hochleistungs-Computing-Szenarien und reagiert auch direkt auf die Herausforderungen bei der Wärmeableitung, die durch die rückseitige Stromversorgungstechnologie (PowerVia) entstehen.

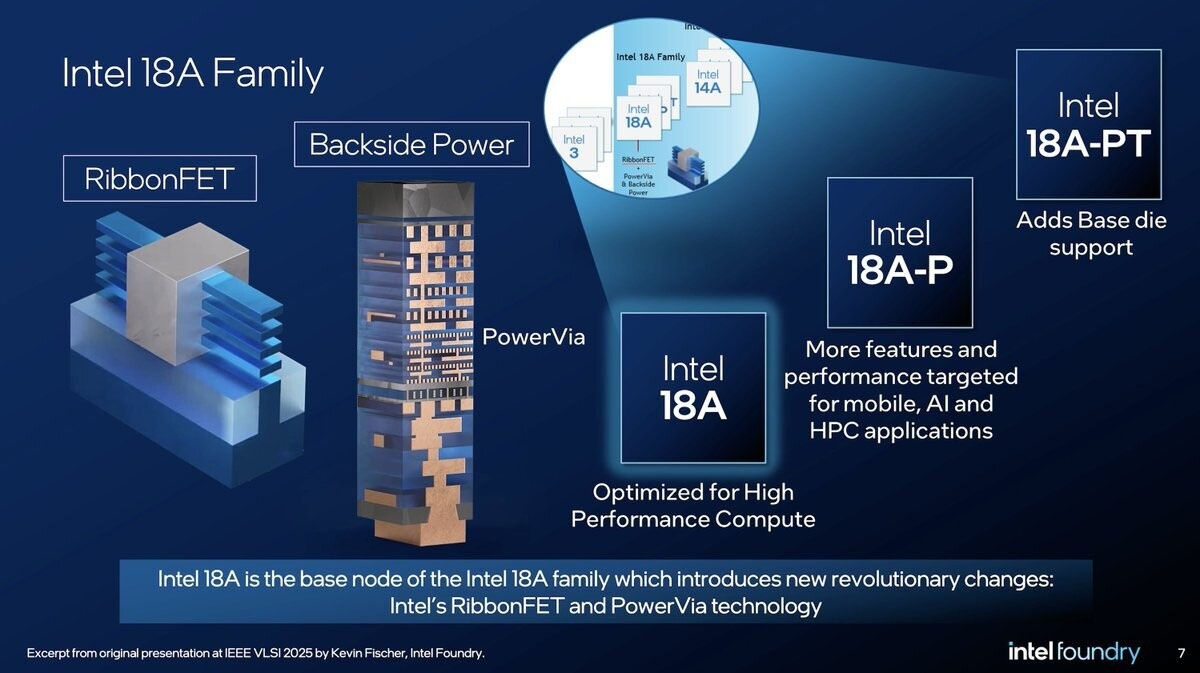

Intel hat Version 1.0 seines PDK-Prozessdesign-Kits für 18A-P an potenzielle Kunden ausgeliefert, damit diese mit dem Testen der Chipverifizierung beginnen können. Dieser Prozess basiert immer noch auf der RibbonFET-Allround-Gate-Transistor-Architektur und der PowerVia-Back-Power-Supply-Technologie und ist eine leistungsgesteigerte Version der 18A-Plattform.

Laut TrendForce prüft Apple den Einsatz des 18A-P-Prozesses zur Herstellung von Chips der M-Serie, während Google erwägt, die fortschrittliche Verpackungstechnologie EMIB von Intel zu nutzen, um das TPU v8e-Projekt zu fördern. Ähnliche Produkte könnten bereits 2027 auf den Markt kommen.